发布时间:2025-03-14编辑:国产MOS管厂家浏览:0次

在功率电子系统的轰鸣声中,工程师们正面临着一个关键挑战:如何让并联的MOS管像交响乐团般和谐运作?当你在设计大电流开关电源、电机驱动或光伏逆变器时,**并联使用多个mos管**几乎是必然选择。但你是否注意到,那些看似相同的器件,在并联运行时可能正在上演"各自为战"的混乱戏码?问题的根源往往就藏在那个容易被忽视的栅极处理环节。

## 一、并联MOS管的物理暗战

当我们将多个mos管并联时,理论上它们的导通电阻会以1/N的比例降低。但实验室数据揭示了一个残酷现实:*并联后的实际导通损耗往往比理论值高出15%-30%*。这个差距的罪魁祸首,正是栅极驱动信号的细微差异。

**寄生参数的放大效应**在此刻显露无疑。每个MOS管的输入电容(Ciss)、反向传输电容(Crss)与PCB走线电感共同构成了RLC谐振网络。当驱动信号同时到达各器件时,由布线差异导致的**栅极信号相位差**会引发多米诺效应:最先导通的器件承受更大的电流冲击,形成恶性循环的温度梯度。

## 二、栅极独立驱动的三重防护

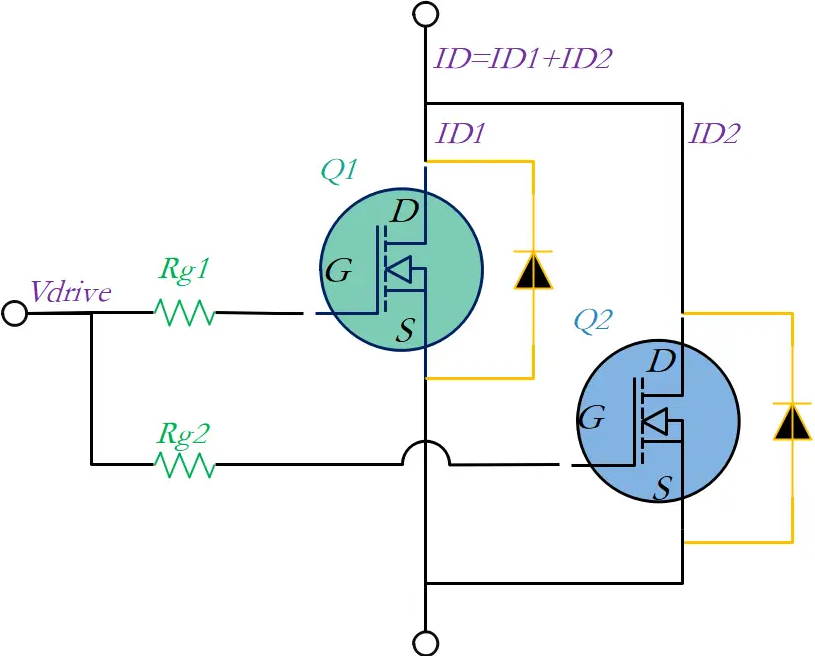

解决这一困局的关键,在于建立**栅极信号的独立控制体系**。我们通过三个维度构建防护网络:

1. **阻抗匹配层**:为每个栅极配置独立的驱动电阻(通常2-10Ω),这相当于给每个"运动员"配备个性化跑鞋。电阻值需通过公式Rg=√(L_trace/(Ciss×N))计算,其中L_trace是走线电感量,N为并联数量。

2. **信号隔离层**:采用星型布线结构,确保驱动信号到各栅极的路径长度误差控制在5%以内。某电动汽车控制器案例显示,将走线差异从15mm缩减到3mm后,开关损耗下降22%。

3. **退耦屏障层**:在每个MOS管的栅源极间并联100pF-1nF陶瓷电容,形成局部储能节点。这相当于为每个器件建立独立"加油站",避免动态工况下的能量哄抢。

## 三、PCB布局的隐形战场

在真实的电路板上,**0.1mm的走线偏差就可能引发灾难**。我们通过四步布局法则化解危机:

1. 采用**同心圆布局**,将驱动IC置于中心,各MOS管沿圆周等距排列。某工业电源测试表明,这种布局使温度分布均匀性提升40%。

2. 栅极走线实施**微带线阻抗控制**,线宽按公式W=0.8×H/(√ε_r×(Z0/87))计算,其中H为介质厚度,Z0目标阻抗通常取50-75Ω。

3. 在功率回路与驱动回路之间建立**电磁隔离带**,最小间距应符合3W原则(走线间距≥3倍线宽)。某光伏逆变器项目采用此方法后,开关噪声降低18dB。

4. **热耦合设计**将相邻MOS管的温差控制在5℃以内。使用热仿真软件计算时,需考虑器件间距与空气对流的非线性关系,间距建议为封装高度的1.2-1.5倍。

## 四、动态均流的进阶技巧

当系统工作在PWM模式下,**开关瞬态的不一致性**会成为新的难题。我们开发出三级补偿策略:

1. **有源门极电压调节**:通过采样每个MOS管的Vds波形,动态调整其栅极驱动电压。某服务器电源采用此法后,均流精度达到±3%。

2. **自适应延时补偿**:利用FPGA实时测量各支路传播延时,数字补偿时间差。实测显示,在100kHz开关频率下,该方法可将时序偏差压缩到200ps以内。

3. **温度-电流闭环**:在每个MOS管源极串入毫欧级采样电阻,结合结温传感器构成双反馈环。某电机驱动器应用案例中,该方法使器件寿命延长3倍。

## 五、实测数据的警示录

在对某型号100A DC/DC模块的失效分析中,我们发现:*未独立处理栅极的并联MOS管组,其MTBF(平均无故障时间)仅为规范值的60%*。深入解析故障波形后,锁定元凶是**栅极振荡引发的热失控**——当驱动信号存在0.5V的差异时,各管子的电流不平衡度竟达到27%。

对比实验更有说服力:在相同工况下,采用独立栅极驱动的模块,其效率曲线在50%负载以上保持平稳,而未优化设计的系统效率则呈现明显"跳水"趋势,在80%负载时差距达2.3个百分点。

## 六、工程师的防错指南

在项目实践中,这些**血泪教训**值得铭记:

- 切勿共用栅极电阻,即使参数完全相同的MOS管批次

- 避免使用单点接地设计,驱动回路与功率回路必须物理隔离

- 警惕Vgs(th)的负温度系数特性,它可能引发雪崩效应

- 动态测试时,务必使用差分探头捕捉ns级的时序偏差

上一篇:隔离变压器驱动mos电路

下一篇:米勒效应烧穿mos管

二维码扫一扫

二维码扫一扫

诺芯盛备案号:粤ICP备2022029173号-4 热销型号:ASDM30C16E-R ASDM3010S-R APM20G02LI AGM311MN